# Delay Asymmetry Correction Model for IEEE 1588 Synchronization Protocol

By

Md. Arifur Rahman

A thesis submitted to the Faculty of Graduate and Postdoctoral Affairs in partial fulfillment of the requirements for the degree of

Master of Applied Science

in

Electrical and Computer Engineering

Carleton University Ottawa, Ontario

© 2013, Md. Arifur Rahman

## Abstract

The thesis proposes a delay asymmetry correction (DAC) model to enhance the IEEE 1588 synchronization protocol. The purpose of this work is to mitigate the effects of unpredictable packet delay variations (PDV), which cause asymmetric link delays on timing packets, in order to improve the synchronization accuracy of the slave clock with respect to the master clock. This is done by computing the time difference between the master and the slave clock in the presence of traffic in a network. The NS-2 results indicate that the proposed solution improves the slave accuracy by measuring the correct offset value in a slave clock for asymmetric communication link delays. The solution results show that the slave clock is able to achieve high synchronization accuracy in the presence of various bi-directional traffic loads, network congestions, and temporary network outage. Furthermore, when there is a routing path change due to the failure in the network, the solution also improves the accuracy of the slave clock with respect to the master clock. However, the proposed solution does not perform well when it is incorporated with the AOCM model.

# Acknowledgements

This thesis would have been impossible without the support and the encouragement I received from several people.

First and foremost I am deeply grateful to my supervisor, Prof. Thomas Kunz for guiding me throughout my masters program and supporting me in every step of the thesis work. His wide knowledge and constructive feedback helped me a great deal.

I would also like to express my deep gratitude to my co-supervisor, Prof. Haward Schwartz and Dr. Mark Wyville (Ericsson, Canada) for their support and invaluable feedback during the thesis research period.

I am also thankful to my colleagues M. Raisul Alam, M. Zulhasnine, and Y. Chang for sharing their experiences and thoughts on various aspects of the scientific research.

Finally, I would like to thank my family for their great support and encouragement throughout this period.

# **Table of Contents**

| A | bstract   |                                                             | ii  |

|---|-----------|-------------------------------------------------------------|-----|

| A | cknowl    | edgements                                                   | iii |

| Т | able of   | Contents                                                    | iv  |

| L | ist of Ta | ables                                                       | x   |

| L | ist of Fi | gures                                                       | xii |

| 1 | Chap      | ter: Introduction                                           | 1   |

|   | 1.1       | Overview                                                    | 1   |

|   | 1.2       | Contributions                                               | 2   |

|   | 1.3       | Outline of the Thesis                                       | 4   |

| 2 | Chap      | ter: Background Information                                 | 5   |

|   | 2.1       | Crystal Oscillators                                         | 5   |

|   | 2.2       | Network Synchronization                                     | 6   |

|   | 2.3       | IEEE 1588: Precision Time Protocol (PTP)                    | 10  |

|   | 2.3.1     | Synchronization Mechanisms                                  | 12  |

|   | 2.4       | IEEE 1588: Factors Affecting Synchronization Performance    | 15  |

|   | 2.4.1     | Asymmetric Delay                                            | 15  |

|   | 2.4.2     | Timing Packet Rate                                          | 16  |

|   | 2.4.3     | Process of Time Stamping                                    | 16  |

|   | 2.4.4     | Oscillator Quality                                          | 17  |

|   | 2.5       | NS-2 Clock Model                                            | 17  |

| 3 | Chap      | ter: Literature Review                                      |     |

|   | 3.1       | Fundamental Limitations of Clock Synchronization            | 20  |

|   | 3.2       | Performance of IEEE 1588: Software Assisted Time Stamping   | 21  |

|   | 3.2.1     | IEEE 1588 Synchronization using a Queuing Estimation Method | 21  |

|   | 3.2.2  | IEEE 1588 Synchronization in a Congested Network: Packet Delay Distribution | n      |

|---|--------|-----------------------------------------------------------------------------|--------|

|   | Estima | ation Method                                                                | 22     |

|   | 3.2.3  | IEEE 1588 Synchronization: Asymmetric Communication Link in Packet Tran     | isport |

|   | Netwo  | ork                                                                         | 24     |

|   | 3.2.4  | IEEE 1588 Synchronization using Fixed Delay Ratio                           | 24     |

|   | 3.2.5  | IEEE 1588 Synchronization: Dynamically Changing Asymmetric Wireless Lir     | ıks 26 |

|   | 3.2.6  | Combined IEEE 1588 and Adaptive Oscillator Correction Model                 | 27     |

|   | 3.3 F  | Performance of IEEE 1588: Hardware Assisted Time Stamping                   | 29     |

|   | 3.3.1  | IEEE 1588v2 Synchronization using Multicast Mechanism in a Packet Networ    | ·k 29  |

|   | 3.3.2  | IEEE 1588v2 Clock Synchronization using Controlled Packets                  | 30     |

|   | 3.4 N  | Motivation                                                                  | 31     |

| 4 | Chapte | er: Proposed Work                                                           | 33     |

|   | -      | Dverview of the Proposed Solution                                           |        |

|   | 4.2 I  | Delay Asymmetry Correction (DAC) Model                                      | 36     |

|   | 4.3 \$ | Supports for Multiple Master Clocks in NS-2                                 | 46     |

|   | 4.4 \$ | Summary                                                                     | 48     |

| 5 | Chapte | er: Simulation Results                                                      | 50     |

|   | 5.1 5  | Simulation Setup                                                            | 50     |

|   | 5.1.1  | Traffic Models Description                                                  | 52     |

|   | 5.1.   | 1.1 Data Centric Traffic Model                                              | 52     |

|   | 5.1.   | 1.2 Voice Centric Traffic Model                                             | 53     |

|   | 5.1.2  | Metrics Collected                                                           | 53     |

|   | 5.1.3  | Slave Clock Synchronization                                                 | 54     |

|   | 5.2 7  | Fest Case with No Traffic                                                   | 54     |

|   | 5.3 T  | Test Cases with Traffic                                                     | 55     |

|   | 5.3.1  | Static Packet Load- with the IEEE 1588 Message Sequences only               | 56     |

| 5.3.1.1      | Description                                                  |                   |

|--------------|--------------------------------------------------------------|-------------------|

| 5.3.1.2      | Results                                                      | 56                |

| 5.3.1.3      | Discussion                                                   |                   |

| 5.3.2 Stat   | tic Packet Load – with the Proposed DAC Model                |                   |

| 5.3.2.1      | Description                                                  |                   |

| 5.3.2.2      | Results                                                      |                   |

| 5.3.2.3      | Discussion                                                   | 60                |

| 5.3.3 Sla    | ve Clock Synchronization with Sudden Large and Persistent Cl | nanges in Traffic |

| Load 63      |                                                              |                   |

| 5.3.3.1      | Description                                                  |                   |

| 5.3.3.2      | Results                                                      |                   |

| 5.3.3.3      | Discussion                                                   | 64                |

| 5.3.4 Sur    | nmary                                                        |                   |

| 6 Chapter: S | ensitivity Analysis                                          | 67                |

| 6.1 Traffie  | c Profile                                                    | 67                |

| 6.2 Effect   | on a Slave Clock with Multiple Master Clocks                 |                   |

| 6.2.1 Des    | scription                                                    |                   |

| 6.2.2 Res    | sults                                                        |                   |

| 6.2.3 Dis    | cussion                                                      |                   |

| 6.3 Effect   | s at Different Parameters                                    | 71                |

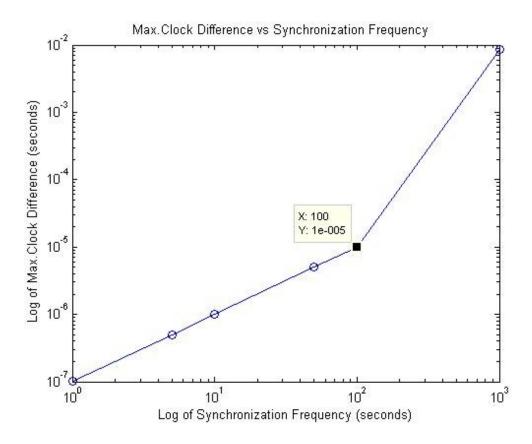

| 6.3.1 IEE    | EE 1588 Synchronization Frequency                            | 71                |

| 6.3.1.1      | Description                                                  | 71                |

| 6.3.1.2      | Result                                                       | 71                |

| 6.3.1.3      | Discussion                                                   | 72                |

| 6.3.2 Slav   | ve Clock Rates                                               |                   |

| 6.3.2.1      | Description                                                  |                   |

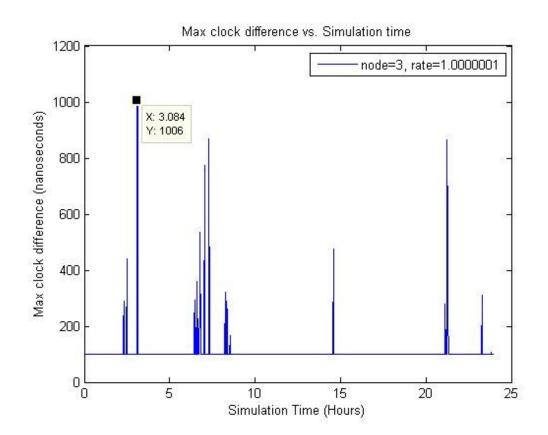

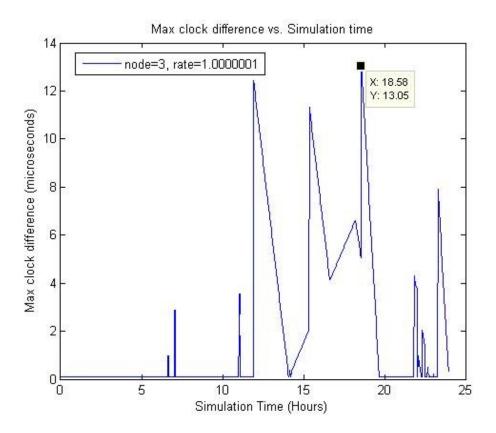

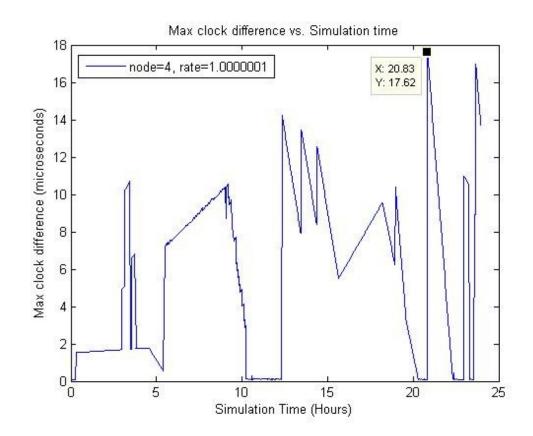

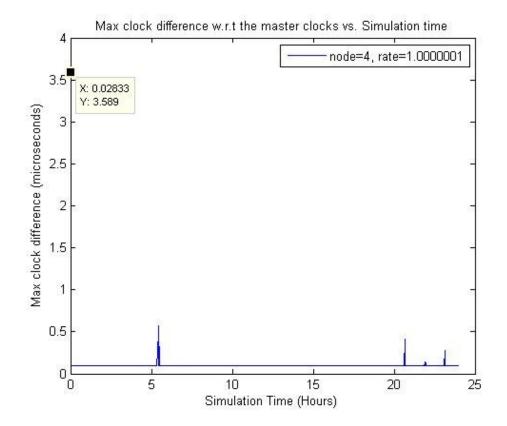

| 6.3.      | 2.2 Result                                                            | 73    |

|-----------|-----------------------------------------------------------------------|-------|

| 6.3.      | 5.2.3 Discussion                                                      | 74    |

| 6.3.3     | Slave Clock Initial Offsets                                           | 75    |

| 6.3.      | 3.3.1 Description                                                     | 75    |

| 6.3.      | 8.3.2 Result                                                          | 75    |

| 6.3.      | 0.3.3 Discussion                                                      | 76    |

| 6.4 7     | Temperature and Aging Effect on a Slave Clock with AOCM               | 77    |

| 6.4.1     | Temperature and Aging Effect on a Slave Clock                         | 78    |

| 6.4.      | .1.1 Description                                                      | 78    |

| 6.4.      | 1.2 Results                                                           | 78    |

| 6.4.      | 1.3 Discussion                                                        |       |

| 6.4.2     | Effect of AOCM on Slave Clock                                         |       |

| 6.4.      | .2.1 Description                                                      |       |

| 6.4.      | .2.2 Results                                                          |       |

| 6.4.      | 2.3 Discussion                                                        |       |

| 6.5 S     | Summary                                                               | 85    |

| 7 Chapte  | ter: Conclusions and Future Work                                      |       |

| 7.1 C     | Conclusions                                                           | 87    |

| 7.2 F     | Future Work                                                           |       |

| Appendice | es                                                                    |       |

| Appendix  | ix A : NS-2 TCL Examples                                              | 91    |

| A.1       | NS-2 TCL Script Code for Data Centric Traffic Model                   | 91    |

| A.2       | NS-2 TCL Script Code for Voice Centric Traffic Model                  | 97    |

| Appendix  | ix B : Additional Test Cases Results for Data Centric Traffic Model   | 104   |

| B.1       | Slave Clock Synchronization with the Slow Change in Network Load over | er an |

| Extren    | mely Long Timescale                                                   |       |

| Descrij  | ption                                                                            |

|----------|----------------------------------------------------------------------------------|

| Results  |                                                                                  |

| Discus   | sion107                                                                          |

| B.2      | Slave Clock Synchronization with the Temporary Network Outages and Restoration   |

|          | 107                                                                              |

| B.3      | Slave Clock Synchronization with the Temporary Network Congestion and            |

| Restora  | ation                                                                            |

| B.4      | Slave Clock Synchronization - Re-route Network Traffic to Bypass One Switch. 112 |

| B.5      | Slave Clock Synchronization - Re-route Network Traffic to Bypass Three Switches  |

|          | 116                                                                              |

| Appendix | C : Test Cases Results with Voice Centric Traffic Model                          |

| C.1      | Slave Clock Synchronization with Static Packet Load for Voice Centric Traffic    |

| Model    | 120                                                                              |

| C.2      | Slave Clock Synchronization with the Slow Change in Network Load for Voice       |

| Centric  | e Traffic Model                                                                  |

| C.3      | Slave Clock Synchronization with the Temporary Network Outages and Restoration   |

| using V  | Voice Centric Traffic Model                                                      |

| C.4      | Slave Clock Synchronization with Temporary Network Congestion and Restoration    |

| using V  | Voice Centric Traffic Model                                                      |

| C.5      | Slave Clock Synchronization with Re-routing Network Traffic to Bypass One        |

| Switch   | using Voice Centric Traffic Model                                                |

| C.6      | Slave Clock Synchronization with Static Packet Load using Multiple Master Clocks |

| for Vo   | ce Centric Traffic Model                                                         |

| Appendix | D: Test Case Result with an Additional Traffic Model – 3                         |

| D.1      | Network Traffic Model - 3 Descriptions                                           |

| D.2      | Slave Clock Synchronization with Static Packet Load for Traffic Model – 3 137    |

# List of Tables

| Table 1: Statistical Data Collected from 'R' Test only                                  | 41  |

|-----------------------------------------------------------------------------------------|-----|

| Table 2: Statistical Data for Static Packet Load                                        | 59  |

| Table 3: Statistical Data for Static Packet Load - Single Run                           | 62  |

| Table 4: Statistical Data for Sudden Large and Persistent Changes in Traffic Load       | 64  |

| Table 5: Statistical Data with Multiple Master Clocks                                   | 70  |

| Table 6: Statistical Data with the Temperature and Aging Effects with the Same Drifti   | ng  |

| Rate                                                                                    | 79  |

| Table 7: Statistical Data with the Temperature and Aging Effects with 100 ppb Faster    |     |

| Drift                                                                                   | 80  |

| Table 8: Statistical Data for the Temperature and Aging Effects with Traffic Profile ar | ıd  |

| 100 ppb Faster Drift                                                                    | 81  |

| Table 9: Statistical data with AOCM                                                     | 84  |

| Table 10: Statistical Data for Slow Changes in Network Load                             | 106 |

| Table 11: Statistical Data for Temporary Network Outage and Restoration                 | 109 |

| Table 12: Statistical Data for Temporary Network Congestion and Restoration             | 111 |

| Table 13: Statistical Data for Re-routing Network Traffic to Bypass One Switch          | 115 |

| Table 14: Statistical Data for Re-routing Network Traffic to Bypass Three Switches      | 118 |

| Table 15: Statistical Data for Static Packet Load – using Voice Centric Traffic Model   | 121 |

| Table 16: Statistical Data for Slow Changes in Network Load – using Voice Centric       |     |

| Traffic Model                                                                           | 124 |

| Table 17: Statistical Data for Temporary Network Outage and Restoration – using Vo      | ice |

| Centric Traffic Model                                                                   | 127 |

| Table 18: Statistical Data for Temporary Network Congestion and Restoration – using    | 5        |

|----------------------------------------------------------------------------------------|----------|

| Voice Centric Traffic Model                                                            | 129      |

| Table 19: Statistical Data for Re-routing Network Traffic to Bypass One Switch – usin  | ng       |

| Voice Centric Traffic Model                                                            | 132      |

| Table 20: Statistical Data for Static Packet Load using Multiple Master Clocks (Voice  | <b>b</b> |

| Centric Traffic Model)                                                                 | 135      |

| Table 21: Statistical Data for Static Packet Load (Traffic Model-3) - using 30% Bursty | у        |

| Traffic                                                                                | 139      |

| Table 22: Statistical Data for Static Packet Load (Traffic Model-3) - using 40% Bursty | У        |

| Traffic                                                                                | 140      |

| Table 23: Statistical Data for Static Packet Load (Traffic Model-3) - using 50% Bursty | У        |

| Traffic                                                                                | 141      |

# List of Figures

| Figure 1: Comparison of the Synchronization Accuracy of NTP, IRIG and IEEE 1588      |                 |

|--------------------------------------------------------------------------------------|-----------------|

| [11]                                                                                 | 9               |

| Figure 2: Basic Synchronization Message Exchange in Delay Request-Response           |                 |

| Mechanism [17]                                                                       | 13              |

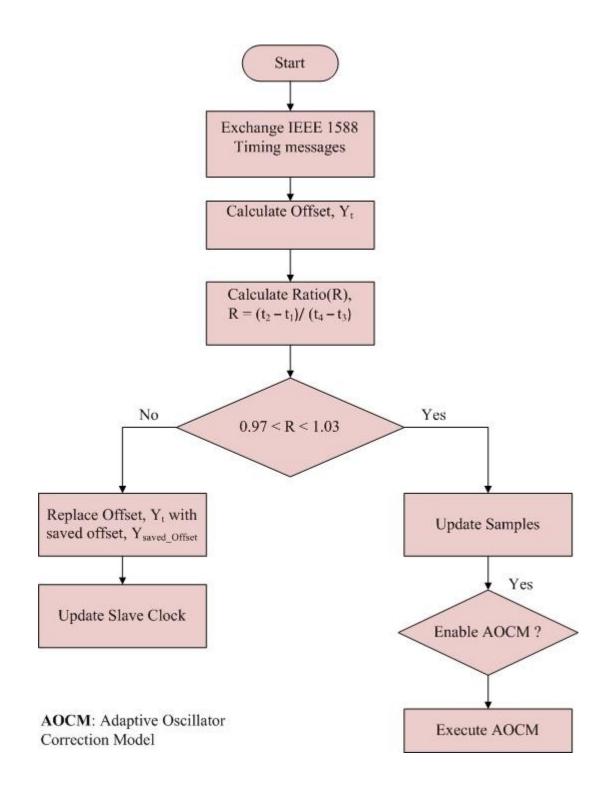

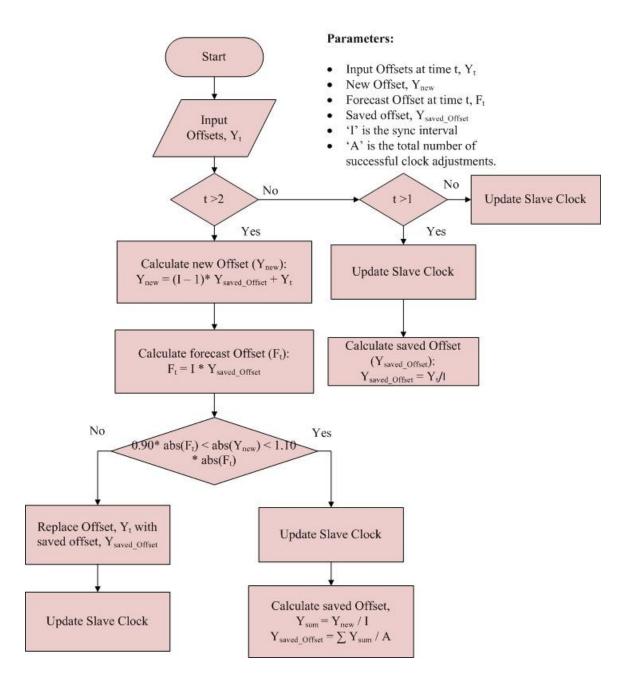

| Figure 3: Flowchart of the Proposed DAC Model                                        | 37              |

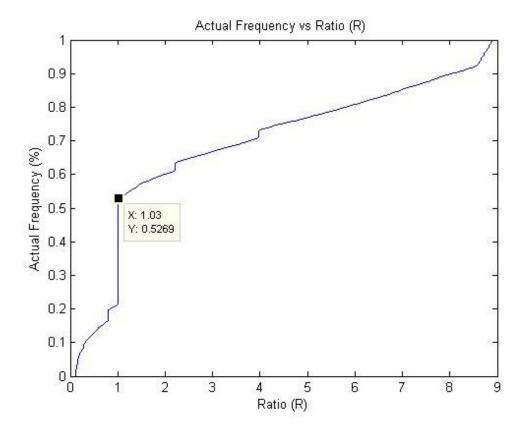

| Figure 4: IEEE 1588 Timing Diagram                                                   | 38              |

| Figure 5: CDF w.r.t the Ratio (R)                                                    | 40              |

| Figure 6: Flowchart of the Update Sample Filter                                      | 44              |

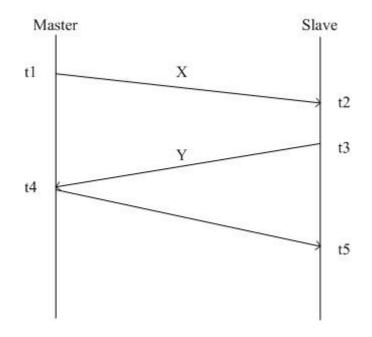

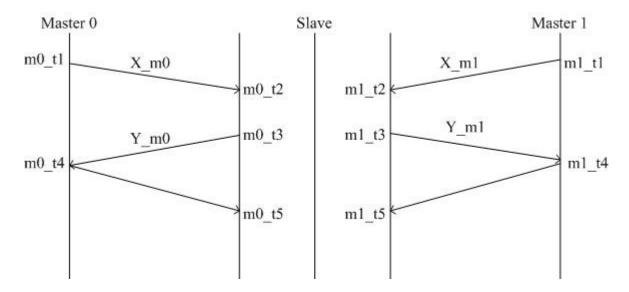

| Figure 7: Timing Diagram for Multiple Master Clocks using IEEE 1588 Messages         | 47              |

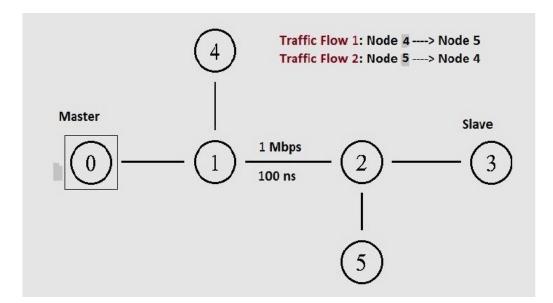

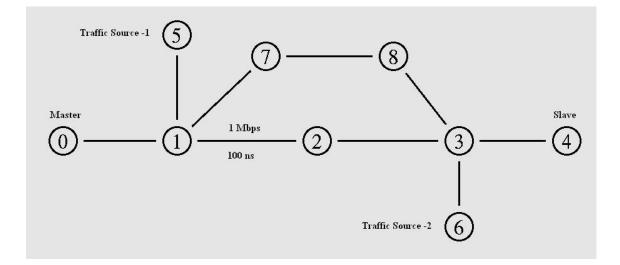

| Figure 8: Network Topology                                                           | 51              |

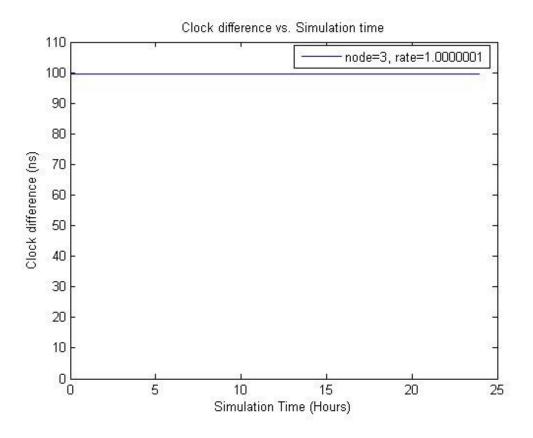

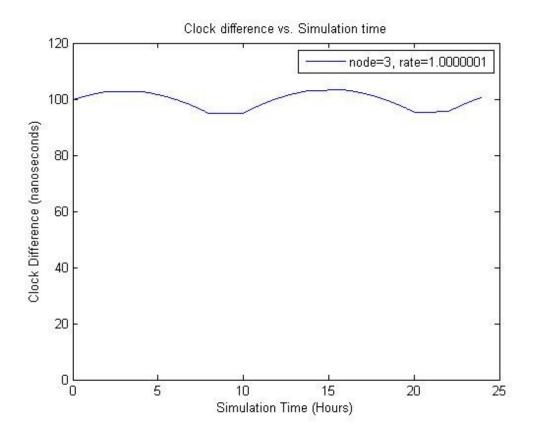

| Figure 9: Slave Clock Accuracy w.r.t the Master clock- No Traffic in the Network     | 55              |

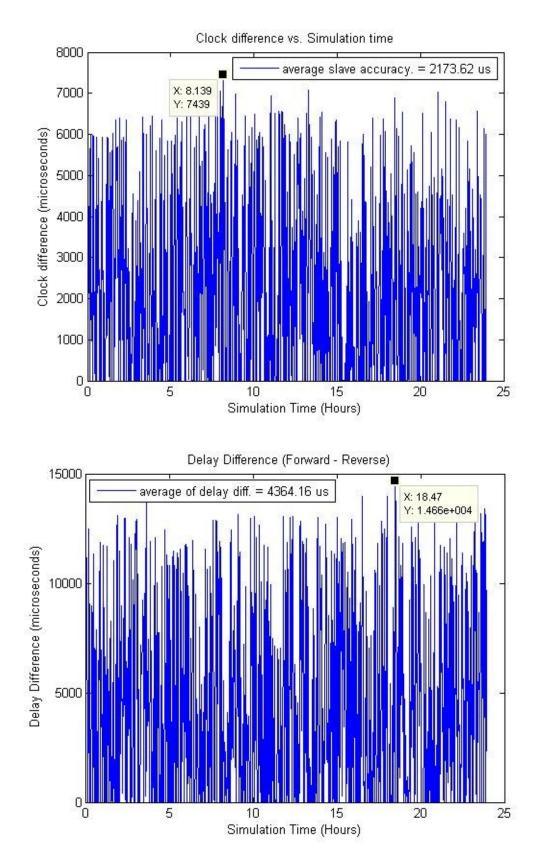

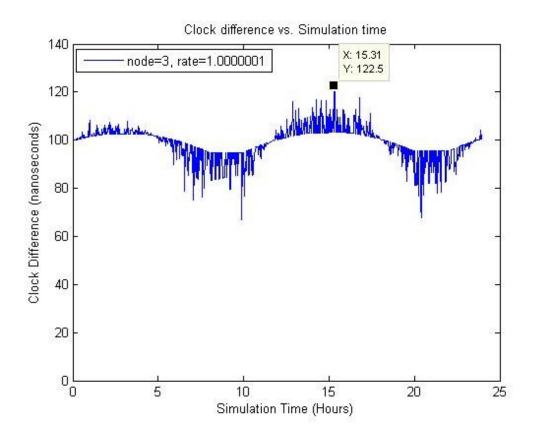

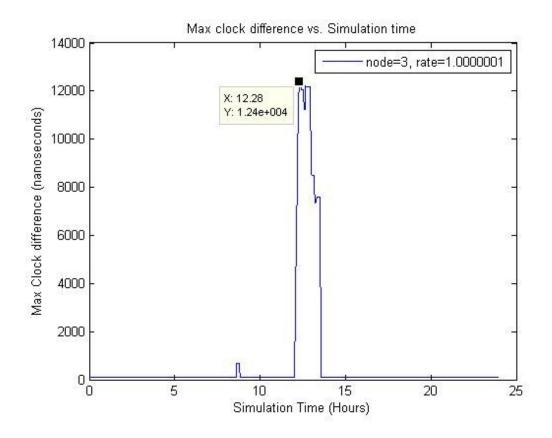

| Figure 10: Slave Clock Synchronization using the IEEE 1588 Message Sequences only    | <sup>,</sup> 57 |

| Figure 11: Slave Clock Synchronization with Static Packet Load-DAC Model Applied     | on              |

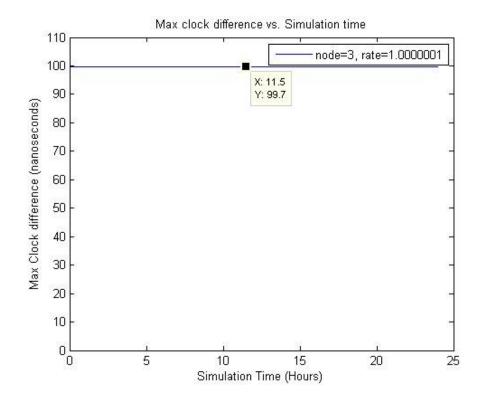

| the Slave Clock                                                                      | 59              |

| Figure 12: Slave Clock Synchronization with Static Packet Load -Single Run           | 62              |

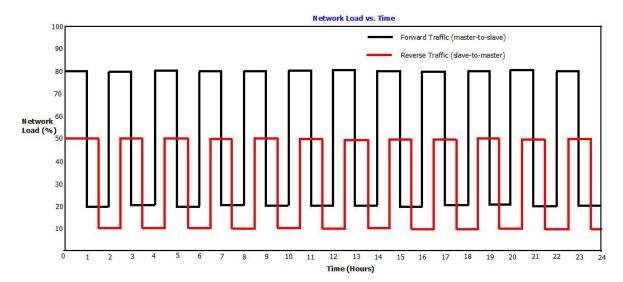

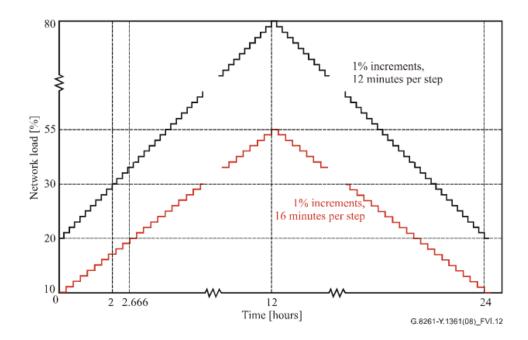

| Figure 13: Load Profile Demonstrating Sudden Large and Persistent Changes in Traffic | 2               |

| Load [3]                                                                             | 63              |

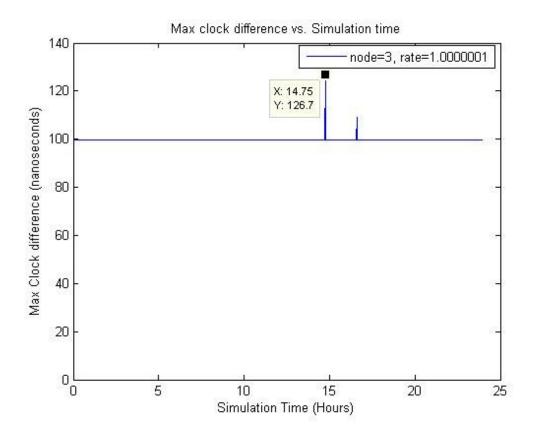

| Figure 14: Slave Clock Synchronization with Sudden Large and Persistent Changes in   |                 |

| Traffic Load                                                                         | 64              |

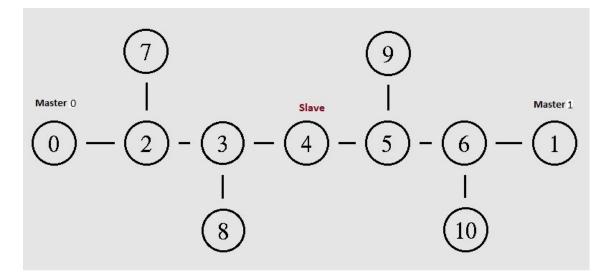

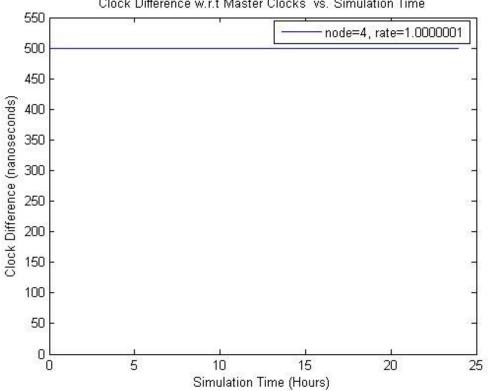

| Figure 15: Network Topology using Multiple Master Clocks                             | 68              |

| Figure 16: Slave Clock Synchronization Accuracy w.r.t both the Master Clocks         | 69              |

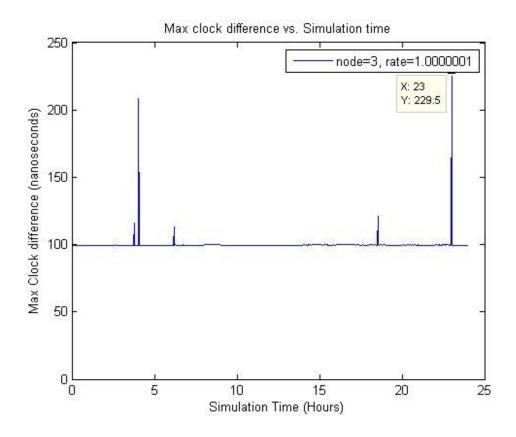

| Figure 17: Effects on Slave Clock Synchronization-Varying IEEE 1588 Synchronization   |  |  |

|---------------------------------------------------------------------------------------|--|--|

| Frequency                                                                             |  |  |

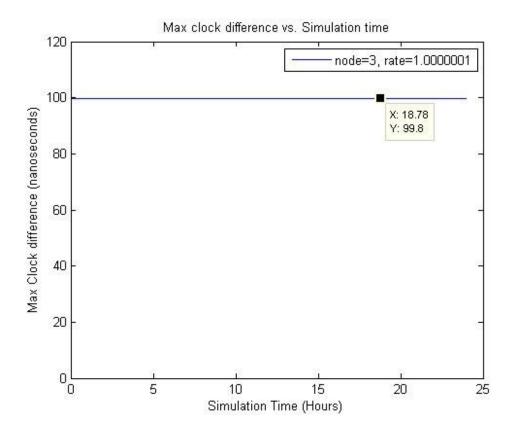

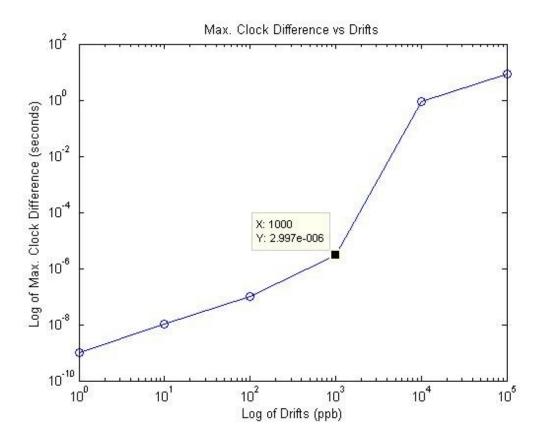

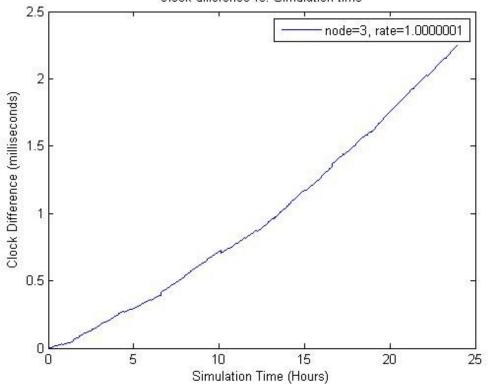

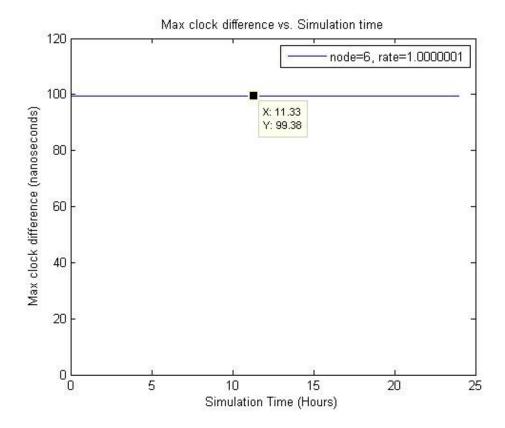

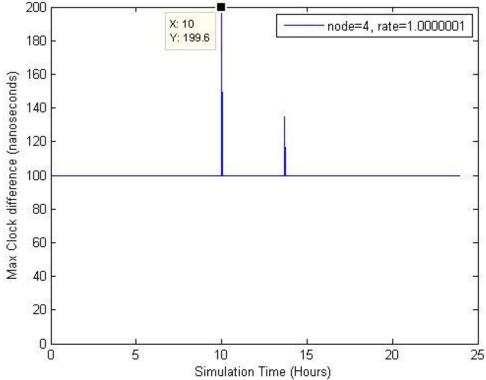

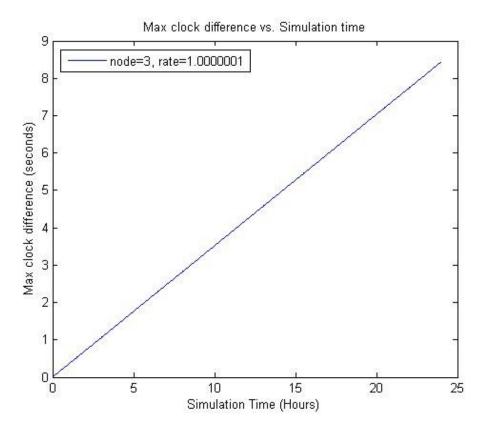

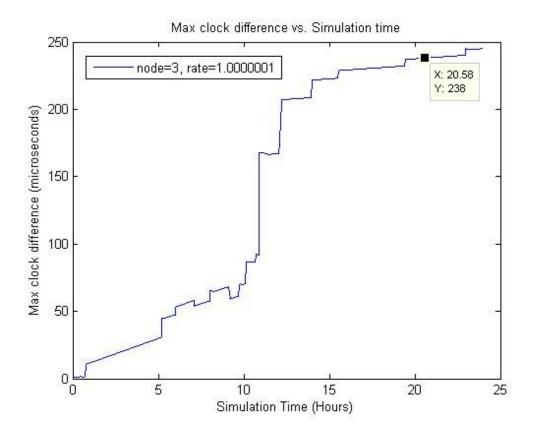

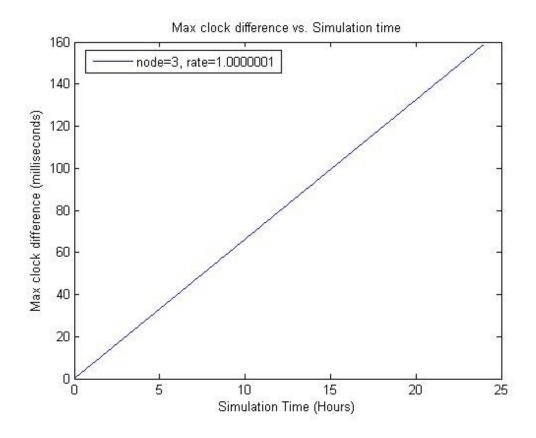

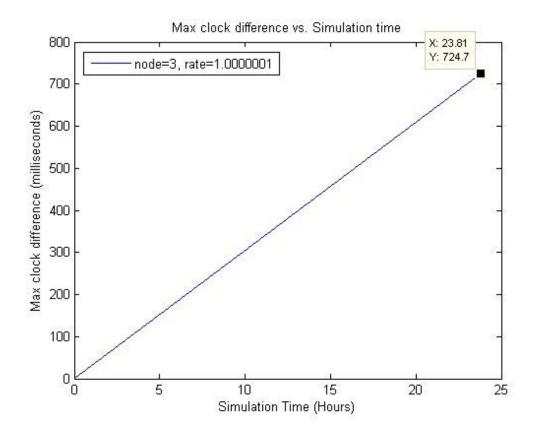

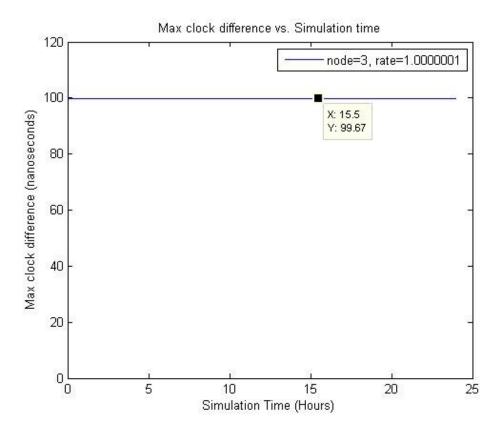

| Figure 18: Effects on Slave Clock Synchronization-Varying Slave Clock Rates           |  |  |

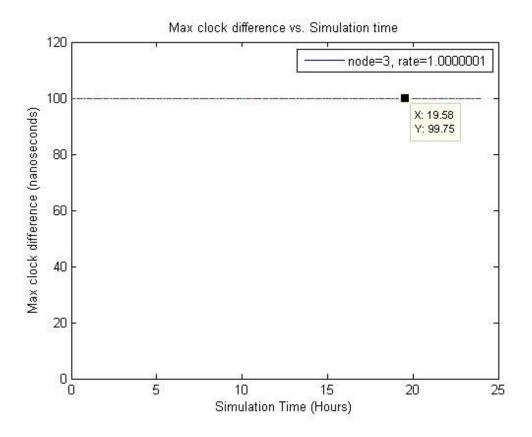

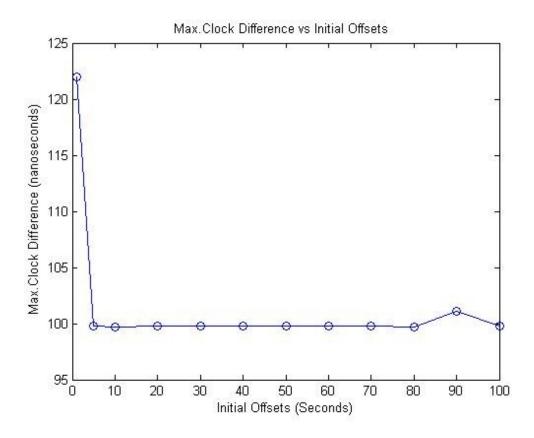

| Figure 19: Effects on Slave Clock Synchronization-Varying Slave Initial Offsets       |  |  |

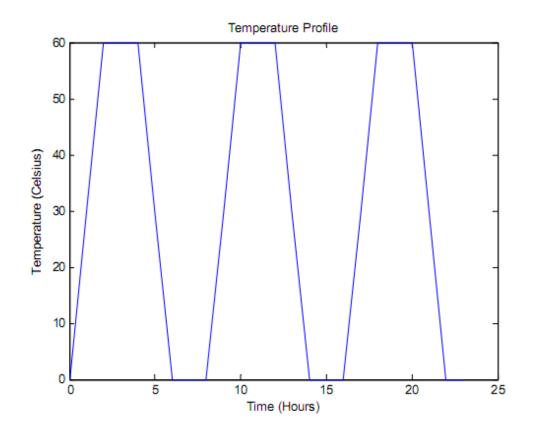

| Figure 20: Temperature Profile [4]77                                                  |  |  |

| Figure 21: Slave Clock Accuracy with the Same Drifting Rate w.r.t the Master Clock –  |  |  |

| Temperature and Aging Effects                                                         |  |  |

| Figure 22: Both Temperature and Aging Effects on the Slave Clock with 100 ppb faster  |  |  |

| Drift                                                                                 |  |  |

| Figure 23: Both Temperature and Aging Effects on the Slave Clock with Traffic Profile |  |  |

| and 100 ppb Faster Drift                                                              |  |  |

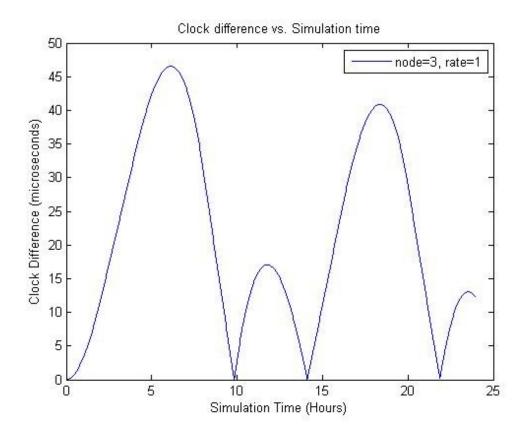

| Figure 24: Slave Clock Synchronization with AOCM Corrections in Locked Mode only      |  |  |

|                                                                                       |  |  |

| Figure 25: Load Profile Demonstrating Slow Changes in Network Load over an            |  |  |

| Extremely Long Time Scale [3]                                                         |  |  |

| Figure 26: Slave Clock Synchronization with Slow Changes in Network Load - using the  |  |  |

| DAC Model                                                                             |  |  |

| Figure 27: Slave Clock Synchronization with the Temporary Network Outage and          |  |  |

| Restoration                                                                           |  |  |

| Figure 28: Slave Clock Synchronization with the Temporary Network Congestion and      |  |  |

| Restoration                                                                           |  |  |

| Figure 29: Network Topology for Re-routing Traffic to Bypass One Switch 113           |  |  |

| Figure 30: Slave Clock Synchronization- Re-route Network Traffic to Bypass One       |

|--------------------------------------------------------------------------------------|

| Switch                                                                               |

| Figure 31: Network Topology for Re-routing Traffic to Bypass Three Switches 116      |

| Figure 32: Slave Clock Synchronization- Re-route Network Traffic to Bypass Three     |

| Switches                                                                             |

| Figure 33: Slave Clock Synchronization with Static Packet Load-using Voice Centric   |

| Traffic Model                                                                        |

| Figure 34: Slave Clock Synchronization with Slow Changes in Network Load -using      |

| Voice Centric Traffic Model                                                          |

| Figure 35: Slave Clock Synchronization with Temporary Network Outage and             |

| Restoration - using Voice Centric Traffic Model                                      |

| Figure 36: Slave Clock Synchronization with Temporary Network Congestion and         |

| Restoration - using Voice Centric Traffic Model                                      |

| Figure 37: Slave Clock Synchronization with Re-routing Network Traffic to Bypass One |

| Switch – using Voice Centric Traffic Model                                           |

| Figure 38: Slave Clock Synchronization with Static Packet Load w.r.t both the Master |

| Clocks -using Voice Centric Traffic Model                                            |

| Figure 39: Slave Clock Synchronization with Static Packet Load -using 30% Bursty     |

| Traffic                                                                              |

| Figure 40: Slave Clock Synchronization with Static Packet Load -using 40% Bursty     |

| Traffic                                                                              |

| Figure 41: Slave Clock Synchronization with Static Packet Load -using 50% Bursty     |

| Traffic                                                                              |

# List of Acronyms

| AOCM   | Adaptive Oscillator Correction Method               |

|--------|-----------------------------------------------------|

| BMC    | Best Master Clock                                   |

| CAPEX  | Capital Expenses                                    |

| DACM   | Delay Asymmetry Correction Model                    |

| E2E TC | End-to-End Transparent Clock                        |

| GPS    | Global Positioning System                           |

| IEEE   | Institute of Electrical and Electronics Engineering |

| IETF   | Internet Engineering Task Force                     |

| ITU    | International Telecommunication Union               |

| IRIG   | Inter-Range Instrumentation Group                   |

| LTE    | Long Term Evolution                                 |

| MTU    | Maximum Transfer Unit                               |

| NGN    | Next Generation Network                             |

| NS     | Network Simulator                                   |

| NTP    | Network Time Protocol                               |

| PDV    | Packet Delay Variation                              |

| РТР    | Precision Time Protocol                             |

| PPB    | Parts Per Billion                                   |

| PPM    | Parts Per Million                                   |

| PPS    | Pulse Per Second                                    |

| QoS    | Quality of Service                                  |

| RAN    | Radio Access Network                                |

| RMS | Root Mean Square           |  |

|-----|----------------------------|--|

| RTE | Residence Time Error       |  |

| RTT | Round Trip Time            |  |

| TCL | Tool Command Language      |  |

| TDM | Time Division Multiplexing |  |

| UDP | User Datagram Protocol     |  |

| UTC | Coordinated Universal Time |  |

# **1** Chapter: Introduction

#### 1.1 Overview

A network consists of computers, routers, switches and other devices, all of which rely on clocks. For a successful communication between these devices, clocks play a significant role in maintaining the same global time across network devices. Now the question arises how these clocks maintain global time with each other. The short answer is synchronizing them. In essence, clock synchronization is setting the time on two or more clocks to be identical. Every node on the network must count time in the same way and every node has to agree when time "zero" occurs [1]. Clocks are typically made from inexpensive oscillator circuits, or battery backed quartz crystals. Each of these clocks tends to drift due to inherent instabilities in the source of oscillator, in addition to environmental factors such as temperature, aging, manufacturer imprecision, air pressure, mechanical pressure etc. [5]. If the network clocks are not synchronized, unexpected things may start to happen: data could be lost, processes could fail, security could be compromised, legal implications could be faced and most importantly the organizations could lose credibility with customers and their business partners [2]. Synchronization requires communications between individual clocks to check whether their deviation is tolerable and whether the clock needs to be corrected. It takes time to go through the process of correcting time and maintaining the accuracy of time relative to another clock. The correction mechanism to synchronize individual clock is a challenging task and is a limiting factor in how accurately two clocks maintain a common time. IEEE 1588v2, known as Precision Time Protocol (PTP) [17], is an industry standard clock synchronization protocol that enables to transfer timing information over packet switched networks. It is widely used both in wire-line and wireless network environments due to its low cost implementations in networked measurement and control systems.

The objective of the thesis is to study different approaches that can be used to synchronize clocks in the network. To understand the problems explicitly, various factors need to be investigated which deteriorate the synchronization accuracy in a network. We propose a solution to achieve high synchronization accuracy. This also involves understanding why the clocks drift, what are the factors affecting the synchronization accuracy, the stability of the clock oscillators, and what can be done to counter those factors.

#### 1.2 Contributions

The contributions of this thesis include the following:

- A Delay Asymmetry Correction (DAC) Model is proposed for the clock synchronization problem. The proposed work aims to enhance the IEEE 1588 protocol by computing the time difference between the master and the slave clock in the presence of traffic in a network. The purpose of this work is to mitigate the effects of unpredictable packet delay variations (PDV), which cause asymmetric link delays on timing packets in order to improve the synchronization accuracy of the slave clock with respect to the master clock. The initiative revolves around the idea of incorporating the DAC model with the conventional IEEE 1588 synchronization protocol.

- The proposed solution further extends to coordinate multiple master clocks through a single slave clock, which may be connected through multiple networks. The rationale of the extension is to support multiple master clocks instead of

selecting a grandmaster clock. The proposed solution ensures that the slave clock receives at least one good offset sample from one of these master clocks within defined update frequency interval for maintaining high synchronization accuracy between the slave and the master clocks.

- The proposed solution also integrates the Adaptive Oscillator Correction Method (AOCM) [4], which is modified to support the proposed DAC model. AOCM is locked to both the master clock and the slave clock that aims to compensate for the temperature and ageing effects of the oscillator and hence, to improve the accuracy and stability of the slave clock during holdover mode.

- The proposed solution is implemented in Network Simulator 2 (NS-2.34), and relies on a two stage filtering methods.

- NS-2 test cases are implemented according to an ITU-T document [3] covering various network loads and network conditions. The test cases are run to evaluate the proposed solution and the results are analyzed.

- The NS-2 results indicate that the proposed solution improves the slave accuracy by measuring the correct offset value in a slave clock for asymmetric communication link delays. The solution results show that the slave clock is able to achieve high accuracy in the presence of various bi-directional traffic loads, network congestions, and temporarily network outage. Furthermore, when there is a change in the routing path due to the failure in the network, the solution also improves the accuracy of the slave clock with respect to the master clock.

However, the slave accuracy deteriorates when the AOCM model is incorporated with the DAC model.

## **1.3** Outline of the Thesis

The chapters of this thesis are organized in the following manner:

Chapter 2 provides background information about the elements affecting the clock accuracy and stability. It reviews different protocols that are commonly used to improve clock accuracy. It also describes the IEEE 1588 protocol including the network factors affecting clock synchronization.

Chapter 3 reviews the state-of-the-art literature related to the performance of IEEE 1588 clock synchronization to account for the delay asymmetry and packet delay variation effects in terms of clock accuracy.

Chapter 4 presents the proposed solution to the clock synchronization problem using the IEEE 1588 protocol. It also discusses the details of the proposed algorithm implemented in NS-2.

Chapter 5 presents the simulation results using the proposed solution from Chapter 4. The test cases are derived from an ITU-T standard document [3].

Chapter 6 scrutinizes the direct effects of various parameters on the slave clock synchronization and provides the analytical explanation.

Chapter 7 concludes the thesis and provides the directions for possible future work.

## 2 Chapter: Background Information

In this chapter, background information related to clock synchronization is presented. The first section of this chapter introduces crystal oscillators, a frequently deployed clock source. This section also discusses the factors affecting the stability and accuracy of a clock oscillator. The second section focuses on different network protocols that can be used to improve clock accuracy, signifying the importance of the IEEE 1588 synchronization protocol in terms of its accuracy. The third section presents the details of the IEEE 1588 synchronization protocol. Section four reviews the elements affecting the clock synchronization accuracy in a network. Finally this chapter is concluded with a brief overview of a clock agent implemented in NS2.

#### 2.1 Crystal Oscillators

Oscillators are an important component of radio frequency and digital devices. The time keeping elements like digital clock, radio, computer, cell phones as well as test and measurement equipment, such as counters, signal generators and oscilloscope are driven by an oscillator stabilized by a crystal resonator. A crystal oscillator is an electric circuit used for generating an electrical signal with a very precise frequency determined by the piezoelectric material. The piezoelectric material converts the electrical impulses to mechanical stress which is subject to the very high mechanical resonances of the crystal and vice versa. The frequency is commonly used to keep track of time to provide a stable clock signal. The clock accuracy and stability depend on the underlying crystal oscillator as frequency source and frequency control components [5]. Furthermore, the degree of frequency stability and the required level of quality of crystal oscillators differ according to the application. The major factors affecting the accuracy of the oscillator are

temperature and aging. Oscillators are inherently not perfect even if there are no temperature and aging effects. An oscillator frequency deviates from its nominal frequency by a given amount, measured in PPM (Part-Per-Million) or PPB (Part-Per-Billion), and the deviation is more pronounced for cheaper oscillators.

Temperature is a significant factor which affects the stability of crystal oscillators. Different angels of crystal cuts produce different frequency-temperature characteristic. In general, it is observed that oscillator frequency stability exhibits a cubic dependency on temperature [6]. The frequency drifts typically are -100ppm to +100ppm for the temperature range of -60°C to +100°C. The term drift refers to several phenomena where a clock does not run at the exact same speed compared to another clock.

Aging is referred as the change of the crystal oscillator frequencies according to the operational time. In general, the aging effect is not linear. However, the aging effect for a short period of time such as 24 h can be considered as linear effect on frequency stability [5, 6]. The frequency drifts due to aging are up to 30ppm for a 25 day period.

#### 2.2 Network Synchronization

Network synchronization ensures that all terminal devices in a network maintain the notion of global time from one source. To achieve such high accuracy clocks, various timekeeping techniques have been studied over the past few decades.

The pioneering work in this area was reading remote clocks in networks, proposed by Dutch scientist Flaviu Cristian in 1989, which deals with unbounded random message delays [7]. The proposed method was useful to improve the precision of both internal and external synchronization algorithms. In this method, each client sends a message to the remote server asking for the current time. Upon arrival of a response, the

sender calculates the round trip time (RTT) as the difference between the transmission and reception times. One of the key features of this algorithm relies on a series of measurements so that at least one measurement encountered the smallest amount of traffic. Logically, the chosen measurement is the one with least RTT.

Another approach was the distributed clock synchronization algorithm, known as Berkley algorithm, developed by Gusella and Zatti at the University of California, Berkley in 1989, discussed in [8]. The method describes the upper and lower bounds on the accuracy of the time synchronization based on a master-slave hierarchy in a local area network. By implementing the algorithm, the results show that it may achieve better synchronization accuracy at a lower cost comparing with other synchronization algorithms till then.

Network Time Protocol (NTP) is one of the most prominent time synchronization methods over four generations of NTP to the present, proposed by Mills and the Internet Engineering Task Force (IETF) group [9]. Initially NTP was designed to distribute time information in a network for systematic dissemination of national standard time throughout the Internet via wire or radio. The latest version of NTP, NTPv4 [10], is widely used to synchronize the local clocks of a computer system over packet-switched networks with variable latency to the order of less than a millisecond or two relative to Coordinated Universal Time (UTC). The main attractive features of NTP are its scalability, robustness to failure, self-configuration in a large multi-hop networks and ubiquitous development. NTP is a layered client-server architecture based on UDP (User Datagram Protocol) messages, which synchronize the clocks in a hierarchical manner. The NTP subnet model introduced a number of widely accessible primary time servers, which are also synchronized by using wire or radio to national standards. The objective of the NTPv4 protocol is to convey timekeeping information from these primary servers to secondary time servers and clients via both private networks and the public Internet. One of the major problems with NTP is that it does not consider network latencies and buffering for precise timing applications. On a NTP-based LAN network, the clock accuracy reduces to 1 to 2 milliseconds due to latency and jitter added by the network devices. The clock accuracy further drops to 1 to 20 milliseconds in NTP-based WAN networks [11]. Furthermore, the latest implementation of NTPv4 does not meet the higher precision requirements for next generation synchronization architecture such as LTE (Long Term Evolution) or 4G wireless backhaul network [12, 13, and 14]. For instance, the deployments of LTE or 4G systems require a time/phase synchronization accuracy within 1µs and frequency synchronization accuracy within 50ppb to 16ppb [15].

One of the emerging alternatives to NTP is the Precision Time Protocol (PTP), defined by IEEE Standard 1588, which was published first in November 2002 [16]. This protocol was originally developed by Agilent Technologies between 1990 and 1998 for testing and industrial automation applications. PTP offers high accuracy and the cost effectiveness of NTP by using existing Ethernet network supporting multicast communications. The protocol makes it possible to achieve synchronization accuracy in the order of sub-microsecond range. A new version of IEEE 1588 was published in 2008 with advanced features and improved performance [17]. The IEEE 1588 protocol overcomes most of the NTP latency and jitter issues through hardware time stamping at the physical layer of the network. It is important to note that the standard performs very well when the network delays are symmetric. As a matter of fact, though, packet network

delays are not symmetric and the one way latency in each direction may be different. In order to minimize the impact of asymmetry, PTP introduced specialized elements known as IEEE 1588 boundary clocks and transparent switches with added functionalities to preserve accuracy [17]. With the addition of boundary clocks or transparent switches, the protocol is able to achieve accuracy in the range of 20 to 100 nanoseconds in a LAN network and less than 10 microseconds in a WAN environment [18]. A comparison of NTP, IRIG (Inter-Range Instrumentation Group) time code and IEEE 1588 is provided in Figure 1 [11, 19]. IRIG provides synchronization over a dedicated cable to carry timing information between IRIG clocks.

| Protocol  | Sync Accuracy         | Interconnect        | Required Clock<br>H/W & S/W       |

|-----------|-----------------------|---------------------|-----------------------------------|

| NTP       | 1-10<br>milliseconds  | Ethernet LAN or WAN | H/W or S/W server,<br>S/W clients |

| IRIG      | 1-10<br>microseconds  | Coaxial Cable       | H/W master and slaves             |

| IEEE 1588 | 20-100<br>nanoseconds | Ethernet LAN        | H/W master and slaves             |

Figure 1: Comparison of the Synchronization Accuracy of NTP, IRIG and IEEE 1588 [11] IEEE 1588-2008 PTP also provides an evolutionary step towards the deployment of the next generation synchronization architecture [15]. Next generation network (NGN) infrastructure combining traditional TDM (Time Division Multiplexing) core networks and packet-based IP backhaul networks based on Ethernet is seen as the future in the telecommunication networks. In addition, there are situations where GPS is not an appropriate synchronization source for traditional synchronization methods particularly for fast-moving objects and in-building Pico-cell applications. PTP is an excellent candidate for GPS backup and as a redundant synchronization source for CDMA/LTE Macro-cells. The PTP system allows for setting/maintaining time/phase synchronization of Radio Access Networks (RAN) such as CDMA, LTE and in-building Pico-cell synchronization. Moreover, IEEE 1588-2008 has been widely studied in various fields such as power distribution networks, wireless sensor network, telecommunications networks, and military applications [20]. The detailed functionalities of IEEE 1588-2008 including the node, system and necessary communication properties to support PTP will be discussed in the next section.

#### 2.3 IEEE 1588: Precision Time Protocol (PTP)

The clocks in a PTP system are structured into a master-slave hierarchy based on time keeping capability and the traceability of its time source. IEEE 1588 PTP aims to achieve sub-microsecond synchronization of real-time clocks in components of a networked distributed measurement and control system [17]. The basic principle of PTP is that the most precise clock in the network has the ability to synchronize all other clocks. The most precise clock is the master clock, which determines the reference time for the entire system; also referred to as Grand Master Clock. The master serves as the reference clock for one or more slave clocks. The process of selecting the master in the network is performed using PTP's Best Master Clock (BMC) algorithm, which is applied by each participating nodes at specific intervals [17]. A master node transmits UDP multicast messages to the slaves at configurable intervals, while slaves respond to the master via unicast messages. Every slave uses the timing information to adjust their local clock with reference to their master.

The synchronization between the master and the slave clock relies on the exchange of timing messages. The standard [17] defines two types of timing messages: event and PTP general messages. Event messages require an accurate timestamp while

10

sending and receiving the event messages. On the other hand, general messages do not require accurate timestamps. The set of event messages consists of

- Sync

- Delay\_Req

- Pdelay\_Req and

- Pdelay\_Resp

The set of general messages include the followings:

- Announce

- Follow\_Up

- Delay\_Resp

- *Pdelay\_Resp\_Follow\_Up,*

- management and

- Signaling.

#### 2.3.1 Synchronization Mechanisms

IEEE 1588 [17] defines two mechanisms for synchronization in a master-slave hierarchy. The first method is called the Delay Request-Response mechanism which uses the PTP event messages. This approach relies on mean delay knowledge, i.e. half of the round trip delay, in order to correct the time difference between two clocks. The second method is the peer delay mechanism which uses Pdelay\_Req, Pdelay\_Resp, and if required Pdelay\_Resp\_Follow\_Up messages. The details of the former approach are discussed as follows.

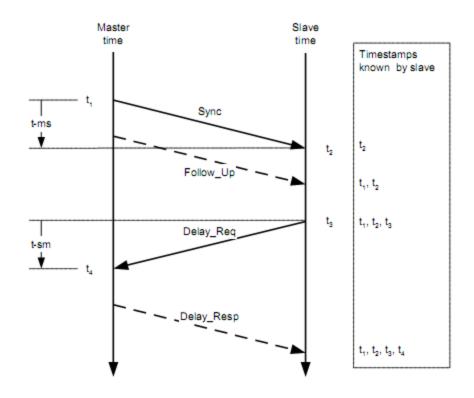

The Delay Request-Response Mechanism is the basic synchronization mechanism in the IEEE 1588 standard to synchronize clocks in a master-slave hierarchy. The basic principle of this method relies on measuring the time difference between the master and the slave clock, which is then used to synchronize a slave to the master clock. Figure 2 shows the basic pattern of synchronization message exchange to synchronize a slave clock to the master clock.

Figure 2: Basic Synchronization Message Exchange in Delay Request-Response Mechanism [17] The message exchange pattern between the master and slave is as follows:

- The master sends a *Sync* message to the slave and notes the transmission time t<sub>1</sub>

- The slave receives the *Sync* message and notes the time of reception t<sub>2</sub>

- The master conveys to the slave the timestamp t<sub>1</sub> by:

- Embedding the timestamp  $t_1$  in the *Sync* message. This requires some sort of hardware processing if highest accuracy and precision are desired.

- Embedding the timestamp  $t_1$  in a *Follow\_Up* message.

- The slave sends a *Delay\_Req* message to the master and notes the transmission time t<sub>3</sub>.

- The master receives the *Delay\_Req* message and notes the time of reception t<sub>4</sub>.

• The master conveys to the slave the timestamp t<sub>4</sub> by embedding it in a *Delay\_Resp* message.

At the end of this exchange of timing messages, the slave clock possesses all four timestamps  $t_1$ ,  $t_2$ ,  $t_3$ , and  $t_4$ . All these timestamps can be used to compute the offset of the slave clock with respect to the master clock and the mean propagation time of the messages between two clocks, which is the mean of t-ms and t-sm in Figure 2. The mean propagation time and the offset can be calculated using following equations:

Mean Propagation Time =

$$\frac{[(t_2 - t_1) + (t_4 - t_3)]}{2}$$

$$= \frac{[(t_2 - t_3) + (t_4 - t_1)]}{2}$$

$Clock \ Offset(O_s) = t_2 - t_1 - Mean \ Propagation \ Time$

$$=\frac{[(t_2-t_1)-(t_4-t_3)]}{2}$$

The clock offset is directly applied to the time stamp of the slave clock [5], as follows:

$Slave's New Time Stamp = Slave's Old Time Stamp - Clock Offset(O_s)$

The computation of an offset and the propagation time assumes that the master-to-slave and the slave-to-master propagation times are equal. Any asymmetry in propagation time introduces an error into the computed value of the clock offset. The computed mean propagation time also differs from the actual propagation times due to the asymmetry [17].

#### 2.4 IEEE 1588: Factors Affecting Synchronization Performance

IEEE 1588 [17] devices are capable enough for achieving highly accurate clock synchronization. Nonetheless, it is important to recognize the key factors that directly affect the network synchronization performance.

#### 2.4.1 Asymmetric Delay

Asymmetric delay is one of the major sources of error of transferring time from one clock to another. In PTP packet based networks, timing packets are exchanged between the master and the slave clock for the purpose of computing the time difference. If the packet exchange delay on the master-to-slave direction and the slave-to-master direction are identical, the offset can be computed precisely since the delays will cancel each other. Unfortunately, the path delay does vary between the master-to-slave direction and the slave-to-master direction, which is referred to as asymmetric delay. The synchronization accuracy is affected by the asymmetric delays in such a way that the degree of accuracy is one half of the asymmetric latencies. To make it worse, asymmetric delays may introduce by the packet delay variation (PDV), which is very difficult to characterize. Moreover, changes in the routing path on a longer time scale will also introduce differences in latency. These fluctuations will further aggravate the asymmetry problem.

Packet delay variation (PDV) or delay jitter in timing packets is another significant factor that deteriorates the synchronization accuracy severely in the IEEE 1588 system. PDV occurs as a result of queuing delays experienced by the timing packets at switching hubs such as routers, switches, cables and other hardware that exists between clocks. Queuing delays are very much dependent on the traffic load, topology of the

15

network and the path reconfiguration of the network. Packets received on a port are placed temporarily in a queue until they can be sent out. The whole process happens extremely fast unless the forwarding port is busy transmitting data packets. As a result, the fluctuation of queuing delays introduces PDV leading to timing errors in the path between two clocks. Considering the quality of service (QoS) and setting the timing packets to be the highest priority are effective in reducing queuing delay. However, queuing delay due to a single packet that has already started to transmit is unavoidable. In a switching hub with a Fast Ethernet interface, queuing delay varies by up to 122.4 µs if only one packet with a maximum transfer unit (MTU) size of 1518 bytes is in the buffer at the instance of arrival of a timing packet [21]. Another source of timing fluctuation is the equipment needed to translate between communication protocols in the networks [18, 22].

## 2.4.2 Timing Packet Rate

An increase in the rate of timing packets generally increases the synchronization performance but may reduce the effective throughput of a system [23]. More frequent transmission of timing packets might increase the accuracy of synchronization. But it also increases the overhead in the network, particularly when more network traffic exists. On the other hand, shortening the transmission interval leads to diminishing returns. So, the transmission frequency of timing packet is a considerable factor in order to balance between the desired accuracy of synchronization and the achievable throughput.

#### 2.4.3 **Process of Time Stamping**

The time transfer latency problem is associated with processing of timing packets by the operating systems. How and where the timestamps are generated are key factors to affect the time synchronization accuracy. Unlike hardware based time stamping, if the packet exchanges are instantaneous there will be no delay and the time difference can be computed accurately. On the other hand, a software based PTP slave program operates at the application layer of the server. A software based PTP computes the time difference in order to adjust the local clock. When a PTP message traverses the protocol stack in a node, it is queued in the buffer to process, which is a fluctuating value and will affect the synchronization accuracy. To achieve the best possible results, the IEEE 1588 time stamps should be generated in hardware or the timestamp should be captured as close as possible to the hardware or the NIC card [24].

#### 2.4.4 Oscillator Quality

The synchronization accuracy also depends on the drift rate of the local oscillator. Temperature and aging are the major driving factors for oscillator drift as discussed in Section 2.1. Oscillator drift can be mitigated by using higher quality oscillators or by driving time from a more accurate source, such as GPS. However, higher quality oscillators and GPS may not be cost effective in terms of capital expenses, CAPEX. The PTP system must support a higher packet transmission rate in order to alleviate the drift of the local oscillator.

#### 2.5 NS-2 Clock Model

Network Simulator 2 (NS-2) is an open source network simulation tool [25]. NS-2 is one of the prominent tools particularly designed for conducting research in computer communications networks. The primary use of NS-2 is to simulate various types of network protocols such as TCP, UDP, multicast protocols, routing algorithms, traffic source behavior, queue management mechanisms, etc. over wired and wireless

environments. It is an object-oriented, discrete event driven simulator written in C++ and the Otcl language [36]. We choose NS-2 because it facilitates to study network effects elaborately such as network congestion, temporary network outage, network path reconfigurations and many more, which are very difficult to model in other simulation tools, for instance MatLab.

Furthermore, other simulation tools do not have a clock model which is affected by temperature and aging effects. As described in Section 1 of this chapter, a clock oscillator starts to drift due to the environmental changes such as temperature and aging effect. Keeping this in mind, a clock agent is implemented by a prior student in NS2 via a C++ class hierarchy. Our proposed work extends the current model of such a clock agent. The details of the implementation of such a clock agent can be found in [4]. The major features of the implemented clock agent are summarized as follows:

- A basic version of IEEE 1588 synchronization protocol as discussed in Section 2.3.1.1 is implemented in NS-2 using a master-slave hierarchy.

- A clock agent is implemented with an initial value to act as a master or slave clock. The master clock has the ability to synchronize itself to a highly accurate GPS signal with a GPS noise of 20 ns RMS (Root Mean Square) jitter on a 1pps edge. Similarly, a slave clock has the ability to synchronize itself with the master clock using the IEEE 1588 protocol [17].

- The clock agent provides a way to capture the time stamps and natural rates of the clock at a regular interval. The natural rate determines the drifts of the clock w.r.t. to a reference clock, which is affected by temperature and aging effects.

• The implementation also provides the self-correcting Adaptive Oscillator Correction Model (AOCM) for both the master and the slave clock to account for the linear aging effects and linear or quadratic temperature effects, adopted from [26].

The implementation also considers locked and holdover periods for both the master and the slave clocks to reflect a network outage for master-GPS and master-slave connections respectively.

## **3** Chapter: Literature Review

This chapter provides a survey of research literature related to the clock synchronization models and performance of IEEE 1588 clock synchronization. Section 1 will focus on the fundamental limitations for synchronizing clocks over wired and wireless networks. Section 2 will review the performance of IEEE 1588 using only software assisted time stamping. The performance of IEEE 1588 using only hardware assisted time stamping will be discussed in Section 3. Finally, this chapter will be concluded with a motivation for our work in this area.

#### 3.1 Fundamental Limitations of Clock Synchronization

Freris *et al.* [27], and Nikolaos *et al.* [28] analyzed the feasibility of clock synchronization and also characterized the fundamental limitations for synchronizing clocks over wired and wireless network. To study the problem, the authors assumed a simple clock model called affine clock which ran at a constant speed, not necessary with identical speed. Each clock is characterized by its relative speed i.e. skew with respect to a reference clock (i.e. master clock) as well as its offset. In addition, another model is considered for delays as the sum of a transmitter-dependent delay, receiver-dependent delay, and a known electromagnetic propagation delay. The authors only considered noiseless communication, where latencies are deterministic and time-invariant but unknown between any two nodes. Given these assumptions, the uncertainty set is characterized. The authors have shown the following impossibility results:

I. Using one master and one slave clock, it is shown that the determination of unknown clock offsets and link delays, particularly one way latency, is impossible even for the ideal scenario where neither offset nor skews drift with time.

20

- II. When a single master clock coordinates with multiple slaves or a single slave clock coordinates with multiple master clocks, the study showed that it is possible to estimate all nodal skews and round trip times correctly between every pair of nodes. But delays and offsets of the nodes cannot be determined exactly by characterizing the uncertainty set because of (n-1) unknown offsets, where n is the total number of nodes. The authors remarked that the delays can be estimated up to one unknown offset for each node except the reference clock (i.e. master clock).

- III. Even considering causality, i.e. packets cannot be received before they are transmitted, the same results are established as above. It does not reduce the region of uncertainty which is unbounded.

As a remark, the authors mentioned that if there is a known asymmetry in the delays that can be characterized, a unique solution exists. Also, the authors did not consider any temperature and ageing effects in this study.

# 3.2 Performance of IEEE 1588: Software Assisted Time Stamping

This section provides a literature survey related to the software assisted time stamping to assess the performance of the IEEE 1588 protocol.

### 3.2.1 IEEE 1588 Synchronization using a Queuing Estimation Method

T. Murakami *et al* [21] proposed a queuing estimation method by using probing packets to improve the synchronization accuracy with the IEEE 1588 protocol. Synchronization accuracy suffers due to the packet delay variation (PDV), which occurs at the queuing buffer in a switch/ router. The objective of the proposed method is to

estimate the occurrence of delay jitter in timing packets and filtering out the packets with delay jitter. To implement such a technique, a modified message sequence is added to the conventional IEEE 1588 protocol. According to the proposed mechanism, it is assumed that the inter packet gap is  $T_i$ . Occurrence of delay jitter at the i-th packet in the group ( $2 \le i \le Np$ ) is estimated with the following criteria:

$$1.If \left(T_{arr(i-1)} - T_{dep(i-1)}\right) > \partial T \text{ or } \left(T_{arr(i-1)} - T_{dep(i-1)}\right) < -\partial T ;$$

delay jitter occured in the packet.

# 2. Otherwise, delay jitter did not occur in the packet

The threshold  $\partial T$  is selected based on clock resolution and accuracy of the clock. Based on the estimation, the packet that has the smallest transmission delay is used for time adjustment. The authors performed experiments using the OPNET discrete event simulator. To configure the network topology, one master and one slave clock is considered and two switches are employed between the master and the slave clock. As result, it is shown that the accuracy of the slave clock is remarkably improved by using the proposed method. It also reduced the adverse impact of delay jitter on synchronization accuracy. However, the proposed method is effective only if at least some timing packets with no delay jitter are able to reach to the slave nodes periodically. In addition, this work does not deal with temperature and ageing effects.

# **3.2.2 IEEE 1588 Synchronization in a Congested Network: Packet Delay Distribution Estimation Method**

T. Murakami *et al* [32] proposed a packet distribution estimation method to improve clock synchronization with IEEE 1588. In this work, the authors also adopted

the queuing estimation method [21] to suppress synchronization error in a heavily congested network. The proposed work relies on switching between two packet selection schemes, which depend on the defined threshold and window size of a target bin. A packet with no queuing delay is used to adjust the clock. The authors used the OPNET discrete event simulator to evaluate the performance of their packet filter techniques. To explain the network scenario, one master and one slave clock is used and four intermediate switches are employed between the master and the slave clock. The performance of the slave clock is evaluated in the presence of symmetric constant cross traffic, as described in ITU-T G.8261 (traffic model 2) [3]. The estimated result reflects the actual delay distribution which is effective for selecting the mode of distribution. The findings of this experiment are summarizes as follows:

- I. When the mean traffic load is 50%, the slave clock is synchronized with the master clock by using the queuing delay estimation method. When the mean traffic load reached 80%, the slave continued its synchronization by applying the packet delay distribution filtering mechanism.

- II. The proposed mechanism improved the synchronization accuracy in the presence of traffic. When symmetric cross traffic is applied, the fluctuation in timing error is within 5  $\mu$ s. On the other hand, the slave maintains synchronization within 15  $\mu$ s, when asymmetric cross traffic with sudden large changes is applied. The authors mentioned that the clock offset error is around 100  $\mu$ s if the delay asymmetry correction is not applied. In the simulation, initial frequency offset in the slave clock is 1 ppm.

However, similar to [21], the proposed mechanism did not consider temperature and ageing effect that also have adverse impact on clock synchronization accuracy.

# 3.2.3 IEEE 1588 Synchronization: Asymmetric Communication Link in Packet Transport Network

S. Lv *et al.* [33] presented an enhanced IEEE 1588 time synchronization method to estimate the correct offset between the master and the slave clock. Considering the asymmetric latency, the proposed algorithm is based on an additional procedure named *OffsetCorrection* for computing the offset. The proposed *OffsetCorrection* mechanism relies on an additional message exchange added to the conventional IEEE 1588 procedure. The performance of the proposed method is evaluated by simulations with several assumptions: initial offset between master and slave clock is 50 s, the end-to-end delay of master-to-slave direction is 25 ms. Considering the asymmetric delay, the ratios of end-to-end delay of master-to-slave direction and slave-to-master direction range from 1:1 to 8:1. The result shows that the error between the estimated and the ideal value changes from  $0.3 \ \mu$ s to  $2.8 \ \mu$ s. The proposed method also shows better performance with the transparent clock mechanism described in [17]. However, the authors did not consider any standard traffic profile to evaluate the performance of the proposed method. In addition, they also did not consider any temperature and ageing effects.

# 3.2.4 IEEE 1588 Synchronization using Fixed Delay Ratio

Z. Du *et al.* [34] proposed an enhanced end-to-end transparent clock (E2E TC) mechanism with a fixed delay ratio in order to correct the time of the slave clock with respect to the master clock. A transparent clock provides an accurate distribution of the PTP protocol across multiport network components such as bridges, routers and switches.

The E2E TC does not act as a master or slave, but forwards all messages just as a normal switch. The proposed mechanism uses two rounds of message exchange. The rationale of introducing the additional message is to capture the difference between the ideal and real values of the residence time referred as Residence Time Error (RTE). The residence time in a transit node is a random variable uniformly distributed in the range of 200 ns to 1 ms. The proposed approach relies on several assumptions, details will be found in [34]. The performance of the proposed method is evaluated by computer simulations and compared with the traditional approach of the IEEE 1588v2 and the E2E TC scheme defined in the IEEE 1588 standard. The bias error of the slave clock is used to compare the above mentioned algorithms. The bias error is calculated as the difference between the calculated offset and the actual offset. The initial offset and the frequency accuracy of the slave clock are assumed to be 50ms and 100ppm respectively. The network is composed of five E2E TC devices between the master and the slave clock. The fixed delay ratio is set 1.2 to 3, and the upper limits of RTE are set to 100 ns, 1 µs, and 10 µs. The results are summarized as follows:

- I. When the fixed short term frequency stability of the TC clocks is 10 ppb, the maximum bias error of the conventional IEEE 1588 method is about 1ms, and the value of the TC scheme is about 100 ns. In contrast, the proposed mechanism exhibits less than 10 ns bias error.

- II. When the short term frequency stability of the TC clocks varies, the maximum bias error of the proposed approach and TC scheme are about 100 ns, whereas the conventional method displays 1 ms bias error.

However, the proposed method is not compatible with the original standard to ensure the coexistence and smooth evolution. Furthermore, replacing the legacy transit nodes (routers and switches) with a TC device is not a realistic approach in terms of capital expenses, CAPEX.

# 3.2.5 IEEE 1588 Synchronization: Dynamically Changing Asymmetric Wireless Links

S. Lee *et al.* [35] proposed an enhanced IEEE 1588 synchronization algorithm to compensate the offset error due to the dynamically changing data rate of wireless links. The data rate changes dynamically due to the movement of the mobile stations, the shared pipe characteristics of the conventional packet oriented wireless technologies, and the asymmetric duplexing method. The proposed mechanism relies on calculating the asymmetric ratio by introducing several new parameters of a dynamically changing wireless link between the master and the slave clock. In general, conventional cellular base stations allocate the data rate for uplink and downlink based on the available bandwidth, the air condition, and its associated buffers status. In the proposed method, the mobile station stores the data rate for each IEEE 1588 message traversing the wireless switch. The performance of the proposed mechanism is evaluated using computer simulation. The initial offset between the master and the slave clock is 25.2 ns.

The result shows that the bias error of the proposed method is reduced to 1 ps, whereas the bias error of the conventional IEEE 1588 [17] is roughly 100  $\mu$ s. The bias error is calculated as the difference between the calculated offset and the actual offset.

The authors did not consider network congestion and path reconfiguration in the network to evaluate the performance of the proposed approach.

# 3.2.6 Combined IEEE 1588 and Adaptive Oscillator Correction Model

W. Ahmed *et al.* [4] proposed a solution that combines the traditional IEEE1588 protocol and the adaptive oscillator correction model (AOCM). The solution suggests a basic implementation of the IEEE 1588 protocol using the Delay Request-Response mechanism to synchronize the slave clock with respect to the master clock in a network. The solution also extends the AOCM model to train a slave clock locked to the master clock and apply that training model to correct the slave clock during the network outage or temporarily network failure. The extension of the AOCM model to the slave clock also intends to correct the temperature and ageing drifts of the oscillator and thus to improve the accuracy and stability of the clock. Here, using the IEEE 1588 protocol, the calculated offset in a slave clock with respect to the master clock is used to generate a correction signal as well as to train the AOCM model.

To implement such an approach, the IEEE 1588 protocol and the AOCM model for the master and the slave clock are implemented in NS-2. A clock agent is implemented in NS-2 to simulate a real clock having drifts due to temperature and aging effects [4]. To evaluate the performance of this work, test cases from an ITU-T document covering various network conditions and network loads are implemented [3]. The experimental findings are summarized as follows:

I. A slave to master synchronization accuracy of 1  $\mu$ s is achieved after 306 synchronization updates from master to slave clock with 95 % confidence. The results indicate that the more the slave clock rates deviate (positively or

negatively) from the master clock, the worse is the slave accuracy w.r.t the master clock on average and vice versa. It also shows that the higher the IEEE 1588 synchronization frequency, the higher is the slave accuracy w.r.t the master clock and vice-versa.

- II. The proposed solution improves the slave clock accuracy up to 10 times in the absence of traffic in the networks, depending on the length of the slave clock training period.

- III. Considering traffic in the network, the results show that the slave accuracy is affected by the asymmetric latencies such that the degree of accuracy is half of the asymmetric latencies.

- IV. When an asymmetric traffic such as 40% load in the master-to-slave direction and 30% load in the slave-to-master direction is increased to 100% in both directions to cause network congestion, the slave accuracy relatively improves because of relatively less asymmetric latencies.

- V. When there is a network outage and the AOCM corrections are applied on the slave clock, the stability of the slave clock improves compared to the case when the AOCM correction is not applied. However the slave synchronization accuracy remains poor. The results indicate that the slave accuracy decreases as the network outage period increases.

However, the author did not take the initiative to correct the asymmetry latency issue in terms of the slave clock accuracy.

# 3.3 Performance of IEEE 1588: Hardware Assisted Time Stamping

This section provides a literature survey related to the hardware assisted time stamping to evaluate the performance of the IEEE 1588 protocol.

# 3.3.1 IEEE 1588v2 Synchronization using Multicast Mechanism in a Packet

## Network

L. Xie *et al.* [29] proposed a multicast mechanism supported by the hardware over a packet network in order to improve the synchronization accuracy between the master and the slave clock. The proposed method focused on factors such as the location of the time stamps, frequency difference, delay asymmetry and error accumulation, which affects the synchronization accuracy. To implement such an approach, the authors considered all transparent clocks, which are used in the packet network and the master clock provides a stable reference time. The findings of the experiment are summarized as follows:

- I. The slave clock frequency is synchronized to the master clock within 100 ppb after 3 synchronization intervals and the convergence period of the frequency synchronization is roughly 9 s. The frequency stability of the slave clock is about 10 ppb after the convergence period. The result also shows that the PTP starts up and performs initial clock reset after the first 21 synchronization intervals.

- II. The slave clock time is synchronized to the master within 100 ns after 9 s and the convergence period of the time synchronization is roughly 9 s as well. The time offset between the master and slave clock remains within 50 ns after the

convergence period. This is mainly caused due to the frequency difference and delay measurement errors.

The authors did not consider other major factors such as temperature and ageing effects, which affects the synchronization accuracy. The authors also did not mention about the traffic load and the ratio of asymmetric link delays to evaluate the performance of the proposed concept.

#### 3.3.2 IEEE 1588v2 Clock Synchronization using Controlled Packets

B. Mochizuki *et al.* [30] proposed a new mechanism in order to eliminate PDV effects on timing packets. The proposed method relies on a multiplexing process between the IEEE 1588 SYNC packet and the background traffic. The authors assumed that the background traffic source can be back pressured [31] to generate the idle time (i.e. headroom) so that the timing packet does not incur any queuing delay in the network. The idea is to store the background packets in the local buffer by the multiplexing state machine integrated with the master clock and transmit them in a regular way when no SYNC packets need to be transmitted. As the scheduled time of SYNC packet approaches, the state machine starts the gap timer. As soon as the gap timer expires, it suspends background traffic transmission and sends the SYNC packet. The gap timer is calculated by each SYNC packet to make sure the channel is free. The multiplexing state machine is implemented in FPGA. The experimental finding shows that packet delays over a 16 hop network range lie between 28.7 µs and 30 µs with a standard deviation of 170 ns. If the SYNC packet does not have any coordination with the background traffic,

packet delay ranges from 98.5  $\mu$ s to 274.4  $\mu$ s with a mean delay of 215.5  $\mu$ s, and a standard deviation of 30.5  $\mu$ s.

Since real time traffic is unpredictable, there is a possibility that more than 2 background packets are transmitted simultaneously when multiple packets are delayed. The authors did not focus on such situation. Moreover, the performance of the proposed method is evaluated with one traffic source only, which does not model a realistic network scenario.

#### 3.4 Motivation

To conclude from the literature survey, the IEEE 1588 protocol plays a significant role to provide a high degree of accuracy and precision both in wired and wireless networks. Unlike NTP, it has the flexibility either by performing a regular message exchange or enhances itself further using the transparent clocks and/or the hardwareassisted time stamping for high precision and accuracy. From the literature survey, we have observed that various filtering techniques have been investigated to improve the slave accuracy with respect to the master clock in a network. A major focus dealt with asymmetric latencies and PDV, which deteriorates the synchronization accuracy severely. In order to overcome the degradation of synchronization performance, additional messages are appended with the conventional IEEE 1588, which may induce additional overhead. The performance of the IEEE 1588 protocol has been evaluated for a masterslave hierarchy without explicitly looking at the variation of the network conditions such as the variation of bi-directional traffic loads or network congestions, which lead to timing errors between the master and slave clocks. In addition, none of the published work attempted to correct the time difference when routing changes, caused by failure in the network and temporary network outage as well. Furthermore, none of the authors